| null_job | wake_job | move_job | read_job | |

| fast_toggle_job | alt_move_job | flash_job | sleep_job | |

| toggle_job | loop_job | command_job | adc16_job | |

| adc8_job | delay_job | fast_adc_job |

| Schematic | Code | PCB | Assembly |

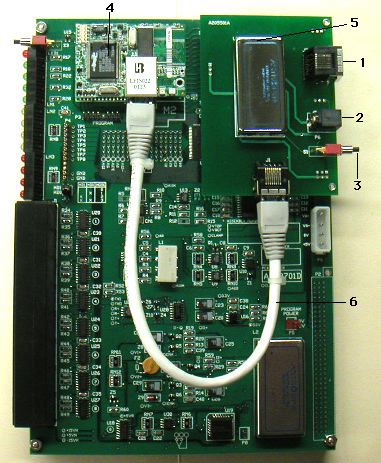

[24-MAR-23] The LWDAQ Driver with Ethernet Interface (A2037E) is a Long-Wire Data Acquisition (LWDAQ) Driver. It provides a LWDAQ Relay and a fully-functional LWDAQ Controller. It comes in a black metal box powered by a single 24-VDC adaptor. The LWDAQ Controller with VME Interface (A3037A) is a fully-functional LWDAQ Controller on a 6U VME-32 card. We can plug twenty A2037A into a VME crate and combined them with a TCPIP-VME Interface (A2064) to create a LWDAQ that reads out a thousand devices. Instructions for setting up and working with all sizes of LWDAQ systems are available in the LWDAQ user manual. The A2037 provides eight LWDAQ driver sockets, each of which may be connected to a LWDAQ device or a LWDAQ multiplexer.

The A2037 provides eight LWDAQ driver sockets. Each socket provides ±15V and +5V power for LWDAQ devices or multiplexers. The A2037 can provide up to 500 mA at ±15V, and 1000 mA at +5V to all its driver sockets combined. It allows you to monitor the power supply voltages, and to measure the total current drawn from them. You can cut off power to the driver sockets by writing to a register on the A2037. Turning the LWDAQ power off for a second, and then on again, resets all devices and multiplexers, and restores them to the sleep state. See the Power Supplies section below for more details.

| Version | Description |

| A | LWDAQ Controller with 6U VME Interface |

| E | LWDAQ Driver with Ethernet Interface |

The analog signal returned from a device to the driver is a low-voltage differential signal with dynamic range ±0.5V. The A2037 can handle this signal in three ways. The first is to pass it through a 10-kHz low-pass filter and digitize it with a 16-bit analog-to-digital converter (ADC). The A2037's adc16 job performs this digitization, stores the result in the driver's random-access memory (RAM), and increments the driver's data address (see Data Address section below) by two (see the Sixteen-Bit ADC section below). The second way to handle the analog signal is to pass it through a 5-MHz low-pass filter and digitize it with an eight-bit ADC. The A2037's adc8 job digitizes the 5-MHz signal, stores it in RAM, and increments the data address. The third way to handle the analog signal is to clamp it when it sits at a zero-level, and then digitize it with the eight-bit ADC when the signal attains its measurement value (see the Eight-Bit ADC section below). The A2037's read job, when applied to a TC255P device, uses its clamp to perform correlated double-sampling of the returned image pixels.

To store measurements, the A2037 provides 512 Kbytes of static RAM. You lose the RAM contents if you turn the A2037 power off, but not if you reset the board or turn off power to the driver sockets. The U1 chip on the A2037 is its programmable logic chip. We describe how to re-program this chip below. Also on the A2037 are sockets for an Ethernet adaptor and a universal serial bus (USB) adaptor (see the Modules section below).

The A2037A provides mounting holes for unlocking levers and a front panel. At the time of writing, we have locking levers and front panels, but they do not appear to fit in most people's VME crates. The push-button switch on the front of the board is the reset switch. Just below it is the reset light, which should go on when you press the switch. You can also reset the board from the VME crate reset line. When you reset the board, you return programmable logic chip to its reset state. But you do not reset the LWDAQ devices to the sleep state. To restore them to the sleep state, you must turn off the LWDAQ power, or go through all the device addresses and transmit a sleep command to each.

The front-panel lamps, all of which are light-emitting diodes (LEDs), have the following functions. The top one is red. It is the reset indicator. The one below is green. It turns on when the A2037 is busy performing an LWDAQ job. The three green lamps below that are driven directly from the LWDAQ power supplies. The top one is connected to +15V, the middle one to +5V, and the bottom one to −15V. If one of these lamps glows dimly, its supply voltage has dropped. If it does not glow, the power is off. Below the green lamps are four yellow lamps and four red ones. These are test-pin lamps, numbered one through eight from the top down (see the Test Pins section below).

We designed the A2037A for the muon end-cap alignment system of the ATLAS detector at CERN. One hundred and twenty A2037As will operate in VME crates in the USA15 room adjacent to the detector hall. In each crate, a VME-TCPIP Interface, such as the A2064 will make all drivers in the crate available over the local ethernet. Seven hundred cables, each up to one hundred meters long will connect these drivers to multiplexers in the detector hall, and cables up to ten meters long will connect these multiplexers to nearly six thousand devices. Prior to installation in ATLAS, however, we intend to use the A2037E for use in ATLAS production and quality assurance fixtures. The A2037E provides an Ethernet with TCPIP interface, which is more convenient for small LWDAQ systems. We used sixteen A2037Es around the rim of the end-cap muon system's Big Wheels so that we could read out the alignment system during assembly on the cavern wall. See here for a picture of an A2037E on the rim of the big wheel, and here for a movie showing the size of the bigg wheel.

A 0x before a numerical value indicates hexadecimal notation. A * before a logic signal name indicates negation. An asserted logic signal is one for which the signal in its name is true. Thus WAKE and *SLEEP are the same signal on a LWDAQ device, but WAKE is asserted when SLEEP is unasserted. A true logic signal is HI, and a false logic signal is LO. A nibble is four bits, a byte is eight bits, a two-byte is sixteen bits, and a four-byte is thirty-two bits. A bit or nibble marked X can take any value without affecting the statement in which it is mentioned. When we respond to address 0x1X, we mean we respond to all addresses 0x10 to 0x1F. An LWDAQ component is one that conforms to the LWDAQ Specification. The target device of an LWDAQ system is the unique device that will receive the next command word from the LWDAQ driver. Circuits made by Brandeis may have the same name, but all have unique assembly numbers. The TC255P Head (A2007) is distinct from the TC255P Head (A2029). They have different assembly numbers.

This manual uses the generic names for all LWDAQ Driver jobs. Instead of clear job we say move job. Instead of transfer job we say alt move job. Instead of expose job we say wake job. Instead of ab expose job we say toggle job.

Suppose we want to set up an instrument consisting of an image sensor, a lens, and an illuminated mask. We pick the Inplane Sensor Head (A2036), and the Inplane Mask Head (A2052) to perform the image capture and mask illumination respectively. Both the A2036 and the A2052 are LWDAQ devices. Each has a single, shielded RJ-45 socket through which it communicates with our A2037. We connect our two devices to our driver with two LWDAQ cables. An LWDAQ cable is simply an eight-way, straight-through, CAT-5 cable.

Our driver and our optical instrument are in separate rooms. The driver is plugged into a VME crate, and we can connect this VME crate to the outside world with the help of a TCPIP-VME Interface (A2064A). The A2064A connects the VME crate to the local 10-Base-T Ethernet. The drivers in the VME crate appear upon the Internet in the same way as a single A2037E would appear on the Internet. The only difference between the two arrangements is that we must specify the VME base address of the VME-resident driver in our data acquisition software. Instead of using an A2064A, however, you may wish to use your own VME interface and write your own software to communicate directly with the A2037A through its registers. Regardless of the computer upon which it runs, and regardless of the interface between the computer and the VME crate, will read and write bytes from the A2037 control and status registers, and read blocks of data out of the A2037 memory. This manual is supposed to provide you with enough information to write your own software to interact with the driver.

We cause the A2037 to perform data acquisition functions, such as flashing a laser or clearing a CCD image area, by writing byte values to its control registers, and we monitor the progress of these functions by reading byte values out of its status registers. When we want to retrieve data from the A2037 memory, we can read it out one byte at a time, or two bytes at a time (but not four bytes at a time). The control registers on the A2037 have names like device job register and device address register.

The data acquisition computer will display and analyze images of our mask. We run our LWDAQ cables from the instrument room to the driver room, and find that they need to be thirty meters long. The LWDAQ can handle solid-core CAT-5 cables up to one hundred meters long with no loss of performance, and braided-core CAT-5 cables up to twenty meters long. Therefore, these cables should be solid-core. They may be shielded or unshielded.

Now we must plug each cable into a socket on the driver. There are eight driver sockets to choose from. We plug the A2036 to the top socket, and the A2052 into the bottom socket. The driver sends commands to only one device at a time, and we call this device the current target device. Each device in an LWDAQ has a device address by which we can select it and make it the target device. The top socket on the A2037 occupies addresses 0x10 to 0x1F. The bottom socket occupies 0x80 to 0x8F. The A2037 assigns sixteen addresses to each socket so that we can use each socket with a sixteen-way multiplexer. In this case, we have no multiplexers, so the sixteen addresses are redundant. For the benefit of our data acquisition software, however, we pick device address 0x10 for the A2036 and 0x80 for the A2052. To select one or other of the devices, we will write these numbers to the A2037's device address register.

Before we can acquire any data from our devices, we must make sure that the A2037A's device power supplies are turned on. For versions 1 through 9 of the A2037A firmware, the A2037A turns on its device power supplies upon a software, hardware, or power-up reset. Starting with version 10 of the firmware, however, the A2037A turns off its device power supplies upon reset. To turn on the power supplies yourself, you must write an odd number to the enable device power register. To turn off the device poweer, you write an even number to the same register.

We consult the A2036 and A2052 manuals. We see that the A2036 is a TC255P Device (type-2) and the A2052 is an LED Device (type-1). In the A2036 manual, we read that we must clear the TC255P of charge with a move job before we can capture an image. Our first step, therefore, is to make the A2036 our target device by writing its device address (0x10) to the A2037's device address register (DAR). After that, we write 2 to the A2037's device type register (DTR), and move_job (2) to the device job register (DJR). The moment we write to DJR, the A2037 begins clearing the TC255P image area. We poll the BUSY bit in the A2037's status register. While BUSY is asserted, the green BUSY light on the driver board lights up. When BUSY is unasserted, we know the A2037 has finished the move job. We call the write to DJR followed by the polling of the BUSY bit a job execution. In the following paragraphs, when we say we "execute job x" we mean that we write x to DJR and poll the BUSY bit until it clears.

Following the instructions in the A2036 manual, we execute a wake_job, which puts the TC255P into the correct state to capture an image. Now we switch to the A2052 manual, and we see that we can flash the LEDs on the A2052 with a flash job. We make the A2052 our target device by writing 0x80 to DAR. We write LED Device (1) to DTR to identify the A2052. We write OUT1 (1) to the device element register (DER) to select the A2052's LED array. We write to the A2037's delay timer the time for which we want the mask to be illuminated. The delay timer counts at 8 MHz, so we express the time as a multiple of the 125-ns clock period. In this case, we want to start by flashing the mask for 10 ms, so we write 80,000 to the delay timer. Now we execute a flash_job (6). The A2037 sets its BUSY bit, flashes the A2052's nine-LED array for 10 ms, and then clears the BUSY bit.

Now that we are finished with the A2052, we return to the A2036 manual, and we see that we must now transfer our image from the TC255P image area into its storage area. We write 0x10 to DAR to make the A2036 our target device, we write 2 to DTR to identify the A2036. We execute an alt move job (5). The alt_move_job moves the TC255P image out of its image area and into its storage area. The image is still inside the TC255P. We set the A2037's data address to zero by writing any value to the Data Address Clear byte. Now we execute a read job (3). The A2037 reads the image out of the TC255P storage area. It reads the image one pixel at a time, at a rate of two million pixels per second, and digitizes them with its 8-bit ADC. At the end of the read_job, the image is in the A2037's memory. The first pixel is a address zero. The last pixel is at address 83935. The first 64 pixels we cannot read out because these overlap the A2037 control registers. But the first 344 pixels of the image are not real image pixels anyway, so we don't care about them. We read the image out of the driver and into our computer via our VME interface, and display the image on the screen.

We decide to add another three mask-lens-sensor instruments to our set-up. Instead of running eight thirty-meter cables, we install an LWDAQ Multiplexer (A2046) in the instrument room, cut up one of our thirty-meter cables into eight short cables, connect all eight of our devices to the A2046, and connect the A2046 to the A2037 using a single thirty-meter cable.

Our software remains the same in all respects, except we must choose new device addresses. Each device address is eight bits long, so there are 256 available addresses. The top nibble of the device address specifies the driver socket connected to the multiplexer, while the bottom nibble specifies the branch socket on the multiplexer. The top socket is socket number one (1), and the bottom socket is number eight (8). On the A2046, the top left socket is number one (1), and the bottom-right socket is number ten (10). If you connect the multiplexer to the second socket from the top on the A2037, and an A2036 to the top-left socket on the multiplexer, the A2036 is at device address 0x21. The 0x2X selects socket number two on the driver, and the 0xX1 selects socket number one on the multiplexer.

Now that we have eight devices driven off the same cable, we must concern ourselves with the voltage drop in the power lines of this cable. We can reduce the power consumption of the combined devices by sending all those we are not using to sleep. When we finish capturing an image from an A2036, we can send it to sleep with a sleep job. We could do the same for the A2052s, but the A2052 is automatically asleep when it is not flashing its LEDs, so we do not have to send it to sleep with a sleep_job. On the other hand, a sleep_job does it no harm.

Plug your LWDAQ Controller with VME Interface (A2037A) into a powered VME crate. We hope that your A2037A comes with a front panel and ejector latches. These make it easier for you to install and remove the board. If you don't have a front panel, then we invite you to ask us to send you one, or you could have your own machine shop make one for you, with the help of this Autocad drawing.

When you plug your A2037A into your VME crate, a red lamp flashes on its front edge. Press the switch on the front of the board. The red lamp turns on. The switch is the reset switch, and the red lamp is the reset indicator. The driver has a second lamp, a green one just below the red one. The green lamp turns on when the driver is busy communicating with or controlling a device.

The driver has a thirty-two bit VME base address and occupies half a megabyte (512 KB) of VME address space. Half a megabyte is eighty thousand in hexadecimal, or 0x80000. The base address must be on an 0x80000 boundary. Addresses such as 0x00280000, 0xF5400000, and 0xB1080000 you can implement with the address switches, but not 0xB0010000.

The driver responds to the following VME cycles, depending upon the setting of switch number twelve on the base address switch (Item One). We ship the boards with LADDR false, or zero (0).

| Switch Twelve | LADDR | Supported Cycles |

| ON | FALSE | 24-bit 1-byte read or write, 24-bit 2-byte read or write |

| OFF | TRUE | 32-bit 1-byte read or write, 32-bit 2-byte read or write |

The switches marked BA31 down to BA19 set bits 31 down to 19 of the A2037's VME base address. When the switch is pushed to the left, its corresponding base address bit is zero (0). You will see a right-pointing arrow on the silk screen above the base address switches that shows you the direction you must move the switch to set the bits to one (1). We ship the boards with base address 0x00E00000 in 32-bit space, and 0xE00000 in 24-bit space. The top eight bits of the base address are used only when you assert LADDR.

Read the section above describing the A2037A in operation, but keep in mind that the A2037E communicates with your data acquisition computer via TCPIP over 10-Base-T Ethernet. So far as your data acquisition software is concerned, its communication with the A2037E takes place over TCPIP. If you would like to write your own data acquisition software, you can do so by sending messages to the A2037E over TCPIP using the A2037E communication protocol described in the A2037E TCPIP Communication Protocol section below. But we recommend you try our own software, which works on MacOS X, Linux, and Windows machines. You will not have to understand the details of how to use most devices, because our software provides instruments that perform the data acquisition for you when you press the acquire button.

We ship the LWDAQ Driver with Ethernet Interface (A2037E) in a black enclosure, as shown below. The configuration reset switch, Ethernet socket, and power socket are at the rear, and the LWDAQ driver sockets, hardware reset switch, and indicator lights are on the front. You should have received a 24-V power adaptor with the A2037E. This provides 24 V DC on a center-negative 5.5-mm power plug. You plug this adaptor into the power socket at the rear.

The A2037E case is made of two piece of black-anodized sheet metal, combined with a dozen screws and standoffs. For details of the case construction, see this archive of Autocad drawings.

The A2037E uses the RCM2200 embedded processor module from Rabbit Semiconductor together with the Ethernet Adapter Piggy Back Board (A2055) to provide the A2037 with a 10-Base-T Ethernet interface. You communicate with the A2037E by TCPIP over Ethernet.

The RCM2200 is a microprocessor module with a TCPIP protocol stack and a 10-BaseT Ethernet socket. We call the RCM2200 the relay because it relays instructions from a data acquisition computer to the A2037E programmable logic chip. The data acquisition computer uses TCPIP over Ethernet to send messages to the relay, and receive messages back again. The messages the relay receives are instructions. The messages it sends back contain data. We describe the structure of these messages in the TCPIP Messages section of the LWDAQ Specification. We provide our own LWDAQ Software that communicates with the A2037E, but you can also write you own.

We call the programmable logic chip on the A2037E circuit board the controller, and its program is the controller firmware. The firmware in the A2037E differs from the firmware in the A2037A because the interface between the controller and the relay differs from that between the controller and a VME back-plane. Nevertheless, by reading from and writing to the same locations in the controller and its associated memory, you operate the A2037E in the same way you operate an A2037A.

The A2037E's Ethernet socket (marked 1 above) connects to the RCM2200 module. This socket is the one you use to connect the A2037E to your local area network with a standard Ethernet cable, or directly to your data acquisition computer with a cross-over Ethernet cable. The power jack (P6, marked 2 above). The first thing you should do when you set up your A2037E is connect power to it and see if the front-panel lights turn on correctly. The power jack is P6 on the Ethernet Adapter (A2055) board.

When you connect power to the A2037E, the red reset indicator (Item One) should light up for a fraction of a second. The green busy indicator (Item Four) should be off, and the three power indicators (Items Five, Six, and Seven) should turn on. When you connect a live Ethernet cable, the yellow LED next to the green LEDs will light up to show an established Ethernet connection. It is the link indicator. The next yellow LED will flicker. It is the activity indicator.

We ship the A2037E with address 10.0.0.37. Consult the Configurator section of the LWDAQ User Manual for instructions on changing the driver's IP address. You can always restore the driver to its factory default settings by pressing the hardwareand configuration reset switches, releasing the hardware switch, and holding the configuration switch for three seconds. The RCM2200 module will re-write its EEPROM to our factory default values.

The A2037E has both software and firmware, both of which must be written to non-volatile memory before the circuit is functional. The software runs in the A2037E's embedded processor, the RCM2200. The firmware runs in the A2037E's main logic chip, U1. The A2037A has only firmware. For our latest software source code, software compiled code, firmware source code, and firmware compiled code, see our Code Directory. The software sources have extension ".c", compiled software is ".bin", firmware sources are ".abl", and compiled firmware is ".jed".

Before you program either version of the A2037, connect power to the circuit. For the A2037E, connect 24V DC to the power socket. For the A2037A, you can plug the board into a VME crage, but access to the programming connectors can be difficult, so we recommend you connect +5V through the programming power connector (Item Thirteen, P5 in the schematic). Pin 1, the top pin, of P5 is 0V, and pin 2 is +5V. Be careful not to apply a voltage higher than +7V or less than -0.7V to P5. (You will damage some of the logic chips on the board if you do, although you will not damage U1.)

The programming connectors are always visible on an A2037A, but you must take the cover off an A2037E enclosure to obtain access to the connectors. For a photograph of the connectors and programming cables all in their correct orientations, see here.

We will start with a description of the firmware programming. The firmware defines all the state machines necessary to coordinate long-wire data acquisition, and also the locations in the A2037 address space of all its control and status registers. One register, at location nineteen, is the firmware version number. If your version is incompatible with a device or multiplexer you are trying to use, you can upgrade the firmware, either by sending the board back to us, or by doing it yourself.

The driver has one programmable logic chip, U1 in the schematic. On a Controller with VME Interface (A2037A), you will find U1 towards the top-right of the board, next to the P1 connector. On a Driver with Ethernet Interface (A2037E), U1 is beneath the piggy-back board that holds the power socket. The chip we use for U1 is the M4A3-512/160 from Lattice Semiconductor. It provides over five hundred programmable flip-flops, and is in-system programmable, which means you do not have to take the 208-pin package off the board to reprogram it.

We program U1 using an eight-way single-row header marked PROGRAM (Item Twelve, P3 in the schematic) allows you to download new firmware into the chip. Pin 5 of this connector has been clipped off. Pin 1 is the left-hand pin, which is the pin closest to the indicator LEDs.

You upgrade the A2037 firmware using Lattice Semiconductor's ispVM software and an ispDOWLOAD Cable, the 8-pin AMP connector version. The software you download for free from Lattice Semiconductor. The cable you can purchase directly from Lattice Semiconductor. The cable plugs into a USB port and costs around $200. The software runs on a Windows PC and Linux.

Install the software and plug the cable into the computer. Run the software and press Scan. The program should tell you it found the cable but there is no power on the target board. Plug the eight-way cable into the board and turn on the board power. Press Scan again. If all is working properly, the program will show you that there is M4A3-512/160 chip on the board in a "JTAG daisy-chain".

Download the new firmware from our Code Directory. The firmware files are named by replacing the leading A in A2037 with a P, and adding a two-digit version number at the end. The version-ten firmware for the A2037A is called P2037A10.jed. The version-eleven firmware for the A2037E is called P2037E11.jed. Thes files are industry-standard JEDEC files. The JEDEC file is a text file, so your browser may display the file directly. You need to save the file to disk so it can be used as the input to the ispVM software. If you want to look at the ABLE source code from which we compiled the JEDEC file, download the same file with a .abl extension instead of .jed.

Once you have the new JEDEC file, go back to the ispVM program and assign the JEDEC file to the programmable logic chip on the A2037. Set the program to "erase, program, verify", and press GO. It takes twelve seconds to program the chip.

Press the reset button. Connect the driver to your DAQ, or plug it into your VME crate, depending upon the type of driver. Check the firmware version number using your DAQ software. Note that upgrading the firmware on an A2037E does not change its TCPIP settings, which are stored in the TCPIP module's EEPROM.

The software in the RCM2200 module provides the TCPIP stack that connects the A2037E to the Internet. We program the RCM2200 with a DB-9 to 10-Pin programming cable we buy from Rabbit Semiconductor. We use software from Rabbit Semiconductor to read a binary file from disk and transfer the binary code to the RCM2200's non-volatile memory.

When we program the RCM2200, we plug the programming cable into the module, as shown here. Only then do we apply power to the A2037E. If we apply power before we plug in the programming cable, the RCM2200 will not respond to the cable. The other end of the programming cable is plugged into a nine-pin serial port on our laboratory Windows PC. We run the Rabbit Field Utility and transfer the latest software to the RCM2200.

We communicate with the A2037E controller by means of its registers alone. We read and write from these registers through the A2037E's TCPIP interface (see below). The A2037E controller provides no diret access to its internal memory. The A2037A, however, provides direct access to its memory through its VME interface, as well as access to most of the registers provided by the A2037E. We read from and write to the A2037E controller memory by means of its RAM Portal. The A2037A also provides a RAM Portal, which our TCPIP-VME Interface (A2064) uses to make multiple A2037As in a single VME crate appear to our LWDAQ Software as if it were an A2037E with multiple sets of eight driver sockets.

The following table gives the byte-by-byte address map of the A2037 controller. In an A2037A, these locations appear in the VME address space at an address we obtain by adding the A2037A's base address (see above) to the location's byte offset, as listed in the table below. In an A2037E, these locations exist at an address equal to their byte offset within the eight-bit interface between the A2037E relay and the A2037E controller.

The driver uses big-endian byte ordering in its address space. The most significant byte of a multi-byte register is the first byte in memory. We will describe each register in more detail in the following sections. The Read-Write column in the table tells you if location's contents can be written, or read from, or both. Note that most of the locations to which you can write cannot be read back.

| Byte Offset (Hex) | Byte Offset (Decimal) | Contents | Read-Write |

|---|---|---|---|

| 00 | 0 | identification number | R |

| 01 | 1 | status register | R |

| 02 | 2 | most recent byte | R |

| 03 | 3 | device job register | RW |

| 05 | 5 | device address register | W |

| 0B | 11 | data address clear | W |

| 0D | 13 | device type register | W |

| 0F | 15 | device element register | W |

| 11 | 17 | loop timer | R |

| 12 | 18 | hardware version number | R |

| 13 | 19 | firmware version number | R |

| 14..17 | 20..23 | delay timer (bytes 3..0) | W |

| 18..1B | 24..27 | data address (bytes 3..0) | W |

| 1D | 29 | enable device power | W |

| 1F | 31 | enable adc8 clamp, delay adc16 count-down | W |

| 20..21 | 32..33 | command register (bytes 1..0) | W |

| 22..25 | 34..37 | repeat counter (bytes 3..0) | W |

| 28 | 40 | configuration switch | R |

| 29 | 41 | software reset | W |

| 2A..2D | 42..45 | reserved for driver base address (bytes 3..0) | W |

| 2E | 46 | reserved for driver address modifier | W |

| 3F | 63 | RAM portal | RW |

| 40 | 64 | first RAM byte | RW |

| 7FFFF | 524287 | last RAM byte | RW |

We describe the function of each register in the sections below. If you are changing over from the Device Driver (A2031), take a look farther down.

The identification byte for the A2037 is 0x25, or 37 decimal. It is the byte at address zero, and you can use it to look for A2037 boards on the 512-Kbyte boundaries of the VME address space. The second byte in the A2037 address space is a status register. Here are the bit functions, with bit zero being the least significant bit.

| Bit | Meaning |

| 7 | Delay Timer Enabled (DTEN) |

| 6 | Transmitting Device Command (TDC) |

| 5 | Transmitting Device Address (TDA) |

| 4 | Repeat Counter Non-Zero (!RCZ, firmware 3+ only) |

| 3 | Device Controller Busy (BUSY) |

| 2 | Sixteen-Bit ADC Converting (BY16, firmware 3+ only) |

| 1 | Loop Timer Enable (LTEN, firmware 3+ only) |

| 0 | Run Settling Delay (RSD, firmware 3+ only) |

You can determine if the A2037 have finished an LWDAQ job by watching the busy bit. The busy bit is set when DJR is not equal to zero. The green busy lamp on the front panel turns on when the busy bit is set.

The most recent byte location contains the byte most recently written to RAM, and you can read it back without disturbing currently-executing data acquisition jobs. The most recent byte register is available only in A2037E code versions 9 and up.

The device job register (DJR) tells the driver to execute a LWDAQ job. See here for a list of LWDAQ jobs supported by the A2037, and the Driver Jobs section of this manual for a description of each supported job and its implementation. When you write your code to communicate with a particular type of device, consult the device manual and it will tell you which jobs you should execute to exercise its DAQ functions.

The device address register (DAR) determines which of the ten device sockets will transmit device commands. Only one driver socket transmits at a time. The top nibble of DAR determines which socket is active. The top socket, the one nearest the reset button, is active when DAR is 0x1X. The bottom socket is active when DAR is 0x8X.

When you write to DAR, the A2037 disables all sockets except the one selected and enables the selected socket. Even if you write the same value a second time, the A2037 waits eight microseconds to allow the driver sockets to stabilize. It then transmits the lower nibble of DAR as a device address through the active driver socket. Devices will ignore this four-microsecond transmission, but multiplexers will receive it and select one of their branch sockets accordingly. The A2037 waits another eight microseconds for the multiplexer's branch sockets to stabilize, and is then ready to begin responding to any pending data acquisition job. While the driver selects a new device, it will accept a new LWDAQ job, but it will report that it is busy executing the job. Therefore, your software does not need to be aware of the delay between writing to DAR and beginning an LWDAQ job, so long as it polls the status or device job registers to decide when the job is done.

In all, therefore, it takes twenty microseconds to select a new device, and the A2037 does not check to see if the new the device address is equal to the previous device address. Doing so would be possible, but would cause problems when you plug a multiplexer into the driver in the middle of continuous data acquisition. If you are watching signals on an oscilloscope, you might see an otherwise inexplicable twenty-microsecond delay between writing to the device job register and the commencement of a device command.

Before you execute a device-dependent job, you must write the target device type to the device type register (DTR).

| DTR | Example Device | Firmware |

| 0 | null | 1+ |

| 1 | LED | 1+ |

| 2 | TC255P | 1+ |

| 3 | Data | 10+ |

| 4 | KAF0400 | 16+ |

| 5 | TC237 | 14+ |

| 6 | ICX424 | 15+ |

| 7 | ICX424Q | 15+ |

| 8 | KAF0261 | 17+ |

The table above gives the device types recognised by the A2037, and the firmware versions that support each type. Device-independent jobs ignore DTR.

When there is more than one sensor or transmitter in a target device, you must write to the device element register (DER) before you execute a device-dependent job. The driver interprets DER depending upon the job you want executed and the target device type. If you want to flash a light source, it selects one of the light sources using the DER. If you want to read an image sensor, it selects one of the image sensors using the DER. Device-independent jobs ignore DER.

After executing a loop job, or any other job that requires the driver to measure the loop time, the loop timer contains an eight-bit number giving the propagation delay in 25-ns units to and from the target device. With a short cable (twenty centimeters), the loop timer will be equal to 0x00. If there is no cable connected to the driver socket, or if the multiplexer or device is not performing the loop-back correctly, then the loop timer will be set to its maximum value, which is 0xF0, or 240 decimal. The signal propagation time along CAT-5 is approximately 5 ns/m each way, or 10 ns/m round-trip. Therefore, the loop counter will increase by one for every 2.5-m increase in cable length.

You can read the A2037 hardware and firmware version numbers out of byte addresses 18 and 19 respectively. The firmware version number tells you which firmware file set was used to program the A2037.

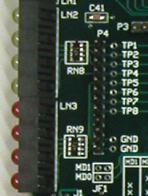

The hardware version is set by the mode jumper field. The MD0 and MD1 connections set the two bits of a two-bit hardware version number. When we connect the MD0 pads together, we set bit zero. When we connect the MD1 pads, we set bit one. Thus we can compose the numbers 0-3 in binary. When the two are left open, the hardware version number is zero. See the Modifications section below for interpretation of the hardware version number.

You set the exposure time for timed jobs, such as flash and toggle, using the delay timer. The timer has four bytes. The upper A2037 ignores the top byte, but you can write a 32-bit number to the timer location. You cannot read back the value of the delay timer, but you can check if it is running by reading the status register. The delay timer counts down with an 8-MHz clock, so each decrement is 125 ns. Write to the delay timer before you execute a flash_job. With the three lower bytes of the four-byte exposure timer set to 0xFFFFFF, we get the longest exposure the timer can support, which is approximately two seconds.

Note that the delay timer is a four-byte location. If you define a four-byte variable in your software, and you are using an A2037A, your VME interface may try to write the location in a single 32-bit data cycle. The A2037A does not respond to 32-bit data writes. It supports only 8-bit and 16-bit data access.

The A2037 on-board memory is a single 10-ns, static RAM chip organized as 512K x 8 bits to provide 512 Kbytes of storage space. The A2037 stores digitized measurements in the RAM location pointed to by the data address. After the A2037 stores a byte in RAM, it increments the data address. You set the data address by writing to the data address location on the A2037. The address counter increments itself whenever the A2037 stores a byte. When the address counter reaches 0x7FFFF, it returns to zero.

The lower sixty-four locations in the A2037A memory space are assigned to control and status registers. If the data address is between zero and sixty-three, the A2037A will store data in inaccessible RAM locations.

Example: During a read job for an A2036, which is a TC255P Type, the A2037A driver transfers an image from the A2036's image sensor into its own memory, storing each pixel at the address counter location and incrementing the address counter afterwards. If, before the read job, we set the data address to zero, the first sixty-four pixels of the image are inaccessible to the VME interface. But the first line of pixels are dummy pixels anyway, so losing the first sixty-four pixels of a dummy line is not a problem.

The LWDAQ Driver with Ethernet Interface (A2037E) does not suffer from the same conflict as does the A2037A.

If you want to clear the address counter to zero, you can also write a zero to the data address clear location. We provide the data address clear location for backward-compatibility with the Device Driver (A2031).

The enable device power bit is the least significant bit in the byte at location 29. In A2037As, this bit resets to 0 on power-up and after either a hardware or software reset. In A2037Es, the enable device power bit resets to 1. When set to 1, the A2037 delivers ±15V and +5V power to the LWDAQ devices. When you write a 0 to the enable device power location, the A2037 disconnects all three power supplies to all its LWDAQ devices and multiplexer. You can use the enable device power bit to force all LWDAQ devices into the sleep state. Write a 0 to the bit, wait five seconds, and write a 1.

The enable clamp bit is the least significant bit in the byte at location 31. It resets to 1 on power-up and after either a hardware or software reset. When set to 1, the eight-bit ADC uses its AC-coupled dynamically-clamped input, which is useful for correlated double-sampling of serial analog data. When set to 0, the eight-bit ADC uses a DC-coupled analog input.

Starting with firmware version 12, the enable clamp bit serves also to control the manner in which the delay timer dictates the sample period of repeated adc16 jobs. When set, the delay timer starts counting down only after the sixteen-bit ADC has finished converting. When cleared, the delay timer starts counting down immediatly the adc16 job begins. The sampling period of the adc16 job will be 375 ns + (125 ns * D), where D is the value you write to the delay timer. In firmware versions 11 and under, clearing the enable clamp bit does nothing to the adc16 job. The delay timer always starts after the adc16 conversion is done.

The Command Register occupies two bytes and represents bits DC1 to DC16 of a LWDAQ command word. The command job transmits these sixteen bits to the target device. The DC16 bit is the most significant bit in the byte at location 32, and DC9 is the most significant bit in the byte at location 33. We arrange the bits in this manner because the A2037 assumes big-endian byte ordering for multi-byte numbers. Thus a two-byte integer will be stored with the most significant byte in the first location, and the least significant byte in the second location. If you have the LWDAQ command word in memory as a 16-bit integer, you can write this integer to location 32 with big-endian byte ordering, and the bits will be in the right place for transmission by the command job.

The controller will execute any job for us multiple times in a row if we write our desired number of executions minus one to the repeat counter. Each time the A2037 finishes a job, it checks the repeat counter. If the repeat counter is zero, the A2037 clears the device job register and enters its rest state. If the repeat counter is not zero, the A2037 decrements the counter and begins executing the same job again. If the job uses the delay timer, the A2037 restores the delay timer to the value it contained at the beginning of the first execution off the job. The A2037 saves a copy of the delay timer whenever we write to the delay timer, and restores the delay timer from this copy when it needs to. After the final repetition of the job, however, the A2037 leaves the delay timer at zero, and clears the delay timer copy as well.

When the repeat counter is one (1), and we write to the device job register, the A2037 executes the specified job twice. The total number of executions is equal to the value of the repeat counter at the beginning of the multiple-execution, plus one. The repeat counter is three bytes long, so its maximum value is 16,777,215 (0xFFFFFF).

When we read from the Configuration Switch location, we get a zero when the configuration swith is depressed, and a one when it is not depressed. The configuration switch exists only on the A2037E. The A2037E relay reads the configuration switch location when it starts up, to see if it should re-write its EEPROM with default configuration values.

You can reset the A2037 programmable logic chip by writing a 1 to the software reset register. The chip will respond as if the hardware reset button on the front of the board had been pressed. Note that on the A2037E, writing to the software reset register does reset the programmable logic chip, but it does not reset the RCM2200 module that manages the TCPIP interface.

When we read a byte from the RAM Portal, we receive the byte in the controller memory at the location pointed to by the Data Address. After we read from the RAM Portal, the controller increments the data address, so that the next read from the RAM Portal will yield the next byte in the controller RAM. The same process works in reverse also, with consecutive bytes in the controller memory being written to through the RAM Portal. The RAM portal exists in all versions of the A2037E firmware, and versions nine and up of the A2037A firmware.

The following table lists the LWDAQ jobs supported by the A2037.

| Job | DJR | DD | Description |

|---|---|---|---|

| null | 0 | no | does nothing |

| wake | 1 | no | wakes up the device |

| move | 2 | yes | moves data within the device |

| read | 3 | yes | transfers data to driver |

| fast_toggle | 4 | no | toggles signal to device |

| alt_move | 5 | yes | alternative move |

| flash | 6 | yes | flashes a transmitter |

| sleep | 7 | no | sends the device to sleep |

| toggle | 8 | yes | toggles a logic signal in the device |

| loop | 9 | no | measures cable loop time |

| command | 10 | no | sends specified command to device |

| adc16 | 11 | no | 16-bit 100 kSPS with storage |

| adc8 | 12 | no | digitizes to eight bits and stores |

| delay | 13 | no | waits for a specified time |

| fast_adc | 15 | no | 8-bit 40 MSPS with storage |

| reserved | 16-63 | reserved for future use |

After you write to DJR, the A2037 begins executing the job and sets the BUSY bit in the status register (bit 3). Your software can determine that the A2037 has finished executing the job either by reading the status register or by reading DJR itself, which will return the job number until the job is done. The busy light on the front of the A2037 lights up when BUSY is set. If you want to stop the A2037 in the middle of a job execution, you can do so by pressing the reset button on the front of the board, or you can write a zero to the DJR and the A2037 will abort the job immediately.

We now describe each of the jobs offered by the A2037. In the case of each device-dependent job, we list the device types for which the A2037 supports the job, and the required firmware version. We refer to the bits in a command word with the notation DC1..DC16.

The null job (0) does nothing. Writing null_job to DJR forces the A2037 to abort any other job execution.

The wake job (1) transmits a device command word containing a one (1) in the WAKE bit (DC8) and zeros in all other bits. The target device should wake up. An obsolete name for wake_job is "expose_job".

The move job (2) is device-dependent, and the A2037 supports it for TC255P devices, for which the job clears the image area of accumulated charge. Another name for the move_job is "clear_job".

The read job (3) is device-dependent. The A2037A and A2037E supports the read job for TC255P devices, for which the job transfers an image from the TC255P storage area into the driver memory, starting at the driver memory address given by the value of the data address register at the beginning of the job. At the end of the job, the data address will point to the byte after the last pixel of the image. The image will be arranged as 244 rows and 344 columns. The image sensor selected by the A2037 depends upon the value of the device element register (DER).

The A2037E firmware 17+ supports readout of the TC255, TC237, KAF-0400, KAF-0261, ICX424, and ICX424Q.

The A2037E with firmware version 9+ supports the read job for data devices, in which the drive synchronizes byte transfer from a device by transmitting stop bits, as described in the Receive Signals section of the LWDAQ Specification. No current version of the A2037A supports byte transfer. The read job, when applied to a data device, sends a single 125-ns LO pulse to the target device and then awaits a low pulse back from the target device of duration 50-ns followed by eight bits of a byte, with the most significant bit first, and each bit taking up 50 ns. These eight bits show up in the serial shift register register, and are stored as a single byte in the driver RAM. For details of the way the driver receives the serial byte, see here.

By means of the repeat counter, you can upload multiple bytes from a target device. You can check the most recent byte received from the data device by polling the most recent byte location. You can either upload a fixed number of bytes from the target device, or you can wait for a particular terminator byte to arrive, and then interrupt the read job by writing a zero to the job register. The uploaded bytes will be in RAM, ready to transfer off the driver.

When the relay reads from the most recent byte register, the controller waits until the read cycle is over before it stores the next uploaded byte in the most recent byte register. The controller must wait, or else it will corrupt the most recent byte value read out by the relay. The relay's read cycle takes of order 1 μs, so each time you read the most recent byte, you introduce a 1-μs pause in the upload of data from a data device.

The one-byte upload from a data device proceeds as follows. First, we write the number three to the device type register and the job register. Within 125 ns of receiving the job number, the controller sends out the falling edge of LO low pulse. The LO pulse lasts for 125 ns and is followed by a rising edge and over 375 ns of HI, thus making a stop bit. Immediately after the rising edge, the controller is ready to receive a serial byte from the data device. It waits until it receives a LO value back from the data device. Once it receives the LO, it waits 75 ns and samples the returned logic value. This value is the most significant bit of the incoming byte, or bit seven. It samples every 50 ns after that, until it has received eight bits. The final bit is bit zero. Once it has the eight bits, the driver waits until the relay is not reading or writing from the controller registers. Occasionally, the relay may be reading the most significant byte register. The controller clocks the eight bits into the most recent byte register, stores the eight bits in RAM, and increments the address counter. These final steps take 125 ns.

The maximum rate at which the driver can upload bytes from a data device occurs during a multiple read job (one for which the repeat counter is non-zero, so the job gets repeated automatically by the controller) during which the relay does not read from the most recent byte, and in which the data device begins transmission of its bits immediately after the rising edge of the driver's LO. Under these circumstances, the driver spends 125 ns in its rest state, 500 ns waiting for the byte, and another 125 ns storing the bytes. The total time for the byte transfer would be 750 ns. Any delay between the rising edge of the driver's low pulse and the data device's response will add to the read time. Such a delay is likely, because the target device must identify the driver's rising edge as part of a stop bit rather than a one or zero bit. This identification will take at least 357 ns. Byte transfer between the A2037E and the A2100 takes place at 1.1 MBytes/s. Each transfer takes 892 ns.

The fast toggle job (4) is identical to delay_job except that the logic signal transmitted to the target device is driven low when the repeat counter has an odd value. When used in conjunction with the delay timer and the repeat counter, the fast_toggle_job transmits a square wave to the target device. The period of this square wave is twice the execution time of a single fast_toggle_job. The execution time of a single fast_toggle_job is 375 ns plus the delay timer value multiplied by 125 ns. Thus the period will be (750 + 250d) ns, where d is the value of the delay timer at the start of the job execution.

The square wave transmitted to the device is not exactly symmetric. The transmitted signal is LO for (125d + 125) ns, but it is HI for (500 + 125d) ns. This assymmetry was not intentional, but the result of an oversight in the design of the firmware.

The alt move job (5) is device-dependent. The A2037 supports it for TC255P devices, for which the job transfers an image from the TC255P image area into the TC255P storage area. Another name for alt_move_job is "transfer_job".

The flash job (6) is device-dependent. The A2037 supports it for TC255P devices and LED devices. In both cases, the job flashes a light source on the device for the length of time specified by the delay timer at the start of the job. The flash time is the delay timer value multiplied by 125 ns. In TC255P devices, the device element register specifies which of four sources to flash, and in LED devices, the same register specifies which of six sources to flash. But the version-two firmware supports only the first source in a LED device, and the version-three firmware supports only the first four sources.

The sleep job (7) transmits a device command word containing all zeros. The target device should go to sleep. The sleep_job takes 4 μs.

The toggle job (8) is device-dependent. The A2037 supports it for TC255P devices, for which the job toggles the TC255P anti-blooming gate input at 125 kHz for a length of time specified by the delay timer at the start of the job. Another name for toggle_job is "ab_expose_job". For more on anti-blooming, see the Anti-Blooming section of the Camera Head (A2056) Manual.

The loop job (9) transmits a device command word containing all zeros except in the WAKE (DC8) and LB (DC7), waits while the returned logic line settles, then transmits a logic low to the target device, and times how long it takes, in 25-ns increments, for the logic low to return to the driver. The A2037 stores this time, which we call the "loop time" in the loop timer location, from you can read it out. The loop_job takes up to 12μs depending upon the length of cable running to the target device.

The command job (10) transmits the sixteen-bit command specified by the command register. The least significant bit of the command register will be DC1, and the most significant will be DC16 . The command_job takes 4 μs.

The adc16 job (11) initiates and waits for a sixteen-bit ADC conversion, and stores the result in the A2037 memory at the location pointed to by the data address at the beginning of the job. At the end of the job, the data address will point to the byte after the second byte of the sixteen-bit ADC output. Note that the A2037 arranges sixteen-bit words in big-endian order, so the most significant byte is the byte at the lower address.

The A2037 pauses for a time determined by the delay timer before it completes the adc16_job. Starting with firmware version 12, the clamp enable bit (CLEN) alters the manner in which the delay timer dictates the sample period of repeated adc16 jobs. For firmware versions <12, and when CLEN is 1, the delay timer starts to count down after the sixteen-bit conversion. This conversion takes roughly 10 μs. The total time taken by the adc16_job is 10 μs + (125 ns * D), where D is the value you write to the delay timer.

Example: We wish to digitize an incoming analog signal at 100 Hz, for 100 s. We write 10,000 to the repeat counter, 80,000 to the delay timer, and 64 to the data address. Then we write 11 to DJR, and the A2037 executes the adc_16 job 10,000 times, each time waiting 10 ms after the conversion is complete before beginning the next execution. We note that the sampling period will be too long by the sixteen-bit conversion time of 10±1 μs, or 0.1%. We might subtract 80 from the value we write to the delay timer to account for this 10 μs. We would still be left with an uncertainty of 0.01% in the sampling rate. The A2037 oscillator is accurate to 50 ppm, or 0.005%.

With firmware version 12+ and CLEN set to 0, the delay timer begins to count down as soon as the adc16 job begins. The sampling period for repeated adc16 jobs will be 375 ns + (125 ns * D), where D is the delay timer value. This formula works so long as the sampling period is greater than 10 μs. Otherwise, the adc16 job waits for its conversion to complete, so the minimum sampling period remains 10 μs. Provided that the sampling period is greater than 10 μs, however, this new method of setting the sampling period allows us to set the period exactly, which is necessary for sinusoid amplitude measurements such as those performed by the Inclinometer Instrument.

Example: We wish to digitize the sinusoid from an Inclinometer Head (A2065), whose period is 854.49 μs. We want to capture a whole number of periods. We set the delay timer to 132 and the repeat counter to 557. The result is samples with period 16.875 μs spanning 9399.375 μs. Eleven cycles of the sinusoid occupy 9399.39 μs, so we are pretty close.

This adc8 job (12) causes an eight-bit ADC conversion and stores the result in the A2037 memory at the location pointed to by the data address at the beginning of the job. At the end of the job, the data address will point to the byte after the result. The adc8_job takes 500 ns plus the time specified by the delay timer at the beginning of the job execution. As with the adc16_job, we can repeat the adc8_job using the repeat counter, and set the sampling rate using the delay timer.

Example: We wish to digitize an incoming analog signal at 1 MHz for a period of 1 ms. We write 999 to the repeat counter, 4 to the delay timer, and 64 to the data address. Then we write 12 to DJR, and the A2037 executes the adc8_job 1,000 times, each time waiting 500 ns after it stores an eight-bit sample, so that the sample rate is exactly 1 MHz.

The eight-bit ADC on the A2037E contains a pipeline for conversion results. The pipeline is four conversions long. The first adc8 job you execute will convert the incoming signal at the time of the adc8 job. But the data that the adc8 job stores in memory is the the data at the end of the pipeline. Thus adc8 job number n creates an eight-bit data value corresponding to sample instant n, but the eight-bit value that gets stored in memory corresponds to sample instant n−4.

The eight-bit ADC will run at up to 40 MSPS when we use it with the fast adc job, and with the adc8 job it will run at a top speed of 2 MSPS. The internal pipeline of the ADC puts a minimum value on the sample rate also. The minimum sample frequency is 10 kHz, which corresponds to a sample period of 100 μs. For slower sample rates, we can use the sixteen-bit ADC.

The delay job (13) simply keeps the A2037 busy until the delay timer counts down to zero. The BUSY bit will be set for 125 ns multiplied by the value of the delay timer at the beginning of the job, plus a constant 375 ns.

The fast adc job (15) performs continuous digitization and storage at 40 MSPS using the A2037's eight-bit ADC. The A2037 continues storing the samples until the delay timer counts down to zero, and stores them in consecutive memory locations, starting at the value pointed to by the data address at the beginning of the job execution. The number of samples stored in memory is approximately equal to the delay timer value at the beginning of the job execution, multiplied by five (there are five 25-ns sampling periods in each 125-ns delay timer clock period).

As with the adc8 job, the samples recorded by the fast adc job are delayed by four places compared to the sample commands. The first four samples recorded in memory will be indeterminate values. The fifth sample recorded will be the one corresponding to the first conversion of the fast adc job.

At the time of writing, the fast adc job is not used by any of the standard LWDAQ Instruments. To test the fast adc job, we use a Toolmaker script that you will find here.

The A2037 uses the ADS7805U sixteen-bit ADC (analog to digital converter). The adc_16 job digitizes the LWDAQ return voltage and stores the two-byte result in memory. The ADC produces a sixteen-bit output representing its ±10-V input range as a two's compliment signed binary value. The gain from the LWDAQ return voltage to the ADC input is 16. The LWDAQ return voltage is the difference between the LWDAQ R+ and R− lines. The dynamic range of the ADC in terms of return voltage is ±0.625 V, which includes the nominal ±0.5 V dynamic range of R defined in the LWDAQ Specification.

| Return (V) | Input (V) | Result (hex) | Result (decimal) |

|---|---|---|---|

| +0.625 | +10.0 | 7FFF | 32767 |

| +0.5 | +8.0 | 6666 | 26214 |

| +0.000019 | 0.000305 | 0001 | 1 |

| 0.000000 | 0.000000 | 0000 | 0 |

| −0.000019 | −0.000305 | FFFF | −1 |

| −0.5 | −8.0 | 999A | −26214 |

| −0.625 | −10.0 | 8000 | −32768 |

You can measure the input noise of the ADC and its amplifiers by selecting device address eight (8 or 0x08). This address selects a reference zero-value for the return voltage using the power monitor circuit. The stochastic noise on this input, as seen by the sixteen-bit ADC, is less than five counts. At the LWDAQ return signal, the noise amounts to less than 100 μV.

The sample_A2037E_adc16 routine in electronics.pas illustrates the use of the sixteen-bit ADC data. The LWDAQ_daq_Diagnostic routine in Diagnostic.tcl shows how the Diagnostic Instrument acquires sixteen-bit ADC samples from an A2037E directly, or from an A2037A through a TCPIP-VME Interface (A2064).

The input of the sixteen-bit ADC is preceeded by a four-pole 10-kHz low-pass filter with a Butterworth response. This filter takes less than a millisecond to settle after a step change, but more than a hundred microseconds. We recommend you allow the filter to settle for a millisecond before you start recording its input. You can obtain the millisecond delay by setting the driver's delay timer and executing a delay job. If you would like to increase the resolution of your measurement, you can take the average of many consecutive samples, which is what the Diagnostic Instrument does when it measures the LWDAQ power supplies.

The 10-kHz low-pass filter (U7 in the schematic) is made of two active filter stages, each of which implements two poles of the filter transfer function. If you want to see the frequency response of our filter, or design your own two-pole or four-pole low-pass filter using the same active filter stages, take a look at our Filter Design Guide.

The A2037 uses the TLV5580 8-bit 80-MSPS ADC from Texas Instruments. The adc8 job digitizes the LWDAQ return voltage and stores the single-byte result in RAM. The input to this ADC passes through either a 5.1-MHz low-pass filter, or through a black-level clamping circuit. By default, the A2037 selects the clamping circuit, which it uses for image readout. You can disable the clamp by writing a zero to the clamp enable location. When the clamp is applied, the ADC digitizes the change in return voltage from its value when the clamp was applied.

The LWDAQ return voltage, R, is the difference between R+ and R−. The ADC accepts inputs from 1.0 V to 2.0 V. An input of 1.0 V yields a result of 0 (0x00) and an input of 2.0 V yields a result of 255 (0xFF). The analog gain from R to the input is 1.0, with a conversion from differential to single-ended. With the clamp turned off, −0.5 V on R becomes 1.0 V at the ADC, for a result of 0x00, while +0.5 V becomes 2.0 V, for a result of 0xFF. Thus the dynamic range of the eight-bit ADC in terms of R is ±0.5V with the clamp turned off. When we use the clamp, the clamp voltage appears as 1.1 V at the ADC input, for a result of 24 (0x18). A voltage 0.9 V higher than the clamp appears as 2.0 V for a result of 255 (0xFF). We shift the clamp voltage to 1.1 V instead of 1.0 V so that we will be sure to see noise above and below the clamp voltage in our images. Thus the black level in our images is not going to be zero, it will be around 24 counts.

The clamp works only when it is pulsed every time we digitize R, and only when the clamping is synchronous with a periodic signal. The image readout jobs, like read_job applied to a TC255 device, perform the synchronous clamping for us, provided that the clamep enable bit is set. But if we want to use the eight-bit ADC for some other purpose, we must clear the clamp enable bit first. Then we execute the adc8 job and read out the result from RAM. The eight-bit ADC is used by both the adc8 job and the fast adc8 job.

The A2037A obtains its power from a VME backplane. It uses the ±12V and +5V supplies. A reset monitor watches the +5V supply, and if the supply drops below +4.75V, the monitor chip forces a hard reset of the driver. With no devices or multiplexers connected to the driver sockets, the A2037A consumes roughly 800 mA from the VME +5V supply and 100 mA at ±12 V. The LWDAQ needs +5V and ±15V. The A2037A generates ±15 V with the FEC15-24D15 DC-DC converter. The A2037A combines the ±12V VME supplies to make a 24V supply for the converter. The converter can supply up to 500 mA at ±15V. For the LWDAQ +5V supply, the A2037A uses the VME +5V supply.

The A2037E obtains its power from a 24-V power adaptor with a 5.5-mm, center-negative power plug. The A2037E input voltage is nomially 24 V, but any voltage between 18 V and 36 V will work fine, provided that the power supply can provide 25 W or more. We plug the power adaptor into the 5.5-mm power jack on the back side of the A2037E. The power plug must be center-negative, not center-positive. Since we designed the A2037E, the industrial standard in power adaptors has settled upon center-positive. We can no longer find center-negative power supplies. If you plug a center-positive power supply directly into the A2037E, it won't power up, but nor will you damage the A2037E or the power supply itself. We buy 24-V center-positive power supplies and switch their polarity with an converter cord. With the converter cord, we can use a power adaptor like the 24-V, 1.3-A MW173KB2403F01.

On the A2037E's piggy-back board, which is itself called the A2055, is a FDC10-24S05 DC-DC converter that takes the 24V power and creates +5V at up to 2000 mA. Meanwhile, on the A2037E board, the FEC15-24D15 takes the 24V power and creates ±15V at 500 mA. With no devices or multiplexers connected to the driver sockets, the A2037E consumes 300 mA from its 24V adaptor.

The self-resetting fuse works well on the A2037A. When you short-circuit the +5V power supply on a LWDAQ device, the fuse cuts off the power to the LWDAQ system, leaving the internal logic of the A2037A intact and responding to VME instructions. But on the A2037E, it turns out that the +5V power supply turns off before the fuse can cut off power. The result is that all logic circuits on the A2037E lose power, and data acquisition stops.

Power to the driver sockets, and therefore to all LWDAQ devices, multiplexers, and repeaters connected to the driver, is controlled by three solid state switches and monitored by current sensing resistors. The +5V power supply is further protected by a 750-mA self-resetting fuse. To turn off the device power, write a zero to the enable device power location. To turn the power on again, write a 0x01 to the same location.

Note: In the original power supply switching circuit slowed down the +5V turn-on by 10 ms using capacitor C39 (see schematic). This slow turn-on led to the long-lasting Reset Failure, which we finally tracked down to C39 in 2010. Drivers that have had C39 removed, which should include both A2037A and A2037E versions, have a blue dot on their serial number label.

In addition to power switching, the A2037 allows you to measure LWDAQ current consumption and power supply voltages. Driver socket zero on the A2037 is a virtual, on-board socket that gives access to ten monitor voltages. To select these voltages, we use device addresses zero through nine. Together, these voltages allow us to calculate the current delivered through the eight driver sockets combined, and the voltage at which it was delivered on the ±15V and +5V power supply lines.

Each monitor voltage differential, so it consists of a differential and common-mode component. The voltage is delivered to the power supply monitor's amplifier, U30. To obtain accurate measurements of the power supply voltages and currents, we must calibrate this amplifier's common-mode and differential gain. We do this with a precision 5-V reference voltage, whose output is available in monitor voltages zero and one. Typical values are −0.020 V/V for common-mode gain and 64 V/V for differential gain.

| DAR | V diff (V) | V com (V) | Description |

| 0 | 5β | 0 | differential gain reference |

| 1 | 0 | +5 | common-mode gain reference |

| 2 | αI1 | V1 | +15 V current measurement |

| 3 | βV1 | 0 | -15 V voltage measurement |

| 4 | αI2/2 | V2 | +5 V current measurement |

| 5 | βV2 | 0 | +5 V voltage measurement |

| 6 | αI3 | V3 | -15 V current measurement |

| 7 | -βV3 | 0 | -15 V voltage measurement |

| 8 | 0 | 0 | grounded common mode input |

| 9 | 0 | 0 | floating common mode input |

We recommend you use the sixteen-bit ADC to measure the voltage presented by each channel. Our lwdaq_A2037_monitor routine, which you will find in electronics.pas, shows how to combine the monitor voltages to calculate the current and voltage of the power supplies. The Diagnostic Instrument takes several hundred measurements of each monitor voltage, and so measures current consumption with 10-μA precision and supply voltage with 1-mV precision.

The power monitor circuit measure the voltage supplied to external devices, so if you turn off the power, you should see these voltages drop slowly to zero. The current measured by the power monitor circuit is the current passing to the external devices, plus the power delivered to the indicator LEDs on the front panel, each of which consumes roughly 6 mA.

The power supply monitors are the basis of the Analyzer Tool, which maintains a database of device current consumption signatures in response to various command words. By comparing the current consumption of actual devices to those of ideal devices, the Analyzer Tool can check for problems in a LWDAQ system, and has proved particularly useful in large systems.

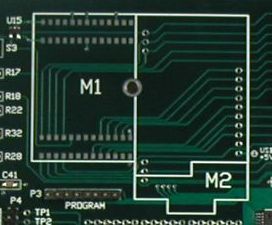

The A2037 provides sockets for two modules. The M1 socket allows you to plug into the A2037 a Rabbit Semiconductor RCM2200 Ethernet microcomputer board. The M2 socket allows you to plug in DLP-USB1 module. In either case, the A2037 will require new firmware to communicate with the adaptor.

The M1 adaptor requires two 26-way surface-mount two-millimeter pitch connectors. The M2 adaptor plugs into the holes provided.

The A2037A is a plug-in replacement for the A2031, but the two boards have several differences of which you should be aware when converting from the A2031. One obvious difference is that the A2037 has only eight driver sockets, while the A2031 has ten. The A2037A does not support the TC255P Sensor Head (A2029). The A2037 has only 512 KB of RAM, while the A2031 has 2 MB. The address switches on the A2037 are vertically-oriented instead of horizontally-oriented, and there are sixteen switches in all, instead of only twelve. The A2037 has two extra board address switches, BA19 and BA20, so that its VME base address can fall on a 512 KB boundary, and take up only 512 KB in the VME address space.

We have changed the name of the A2031 address counter to data address, so that the address counter clear location on the A2031 is now the data address clear location.

There are eight test pins on the A2037 circuit board, connected to the lower eight LEDs on the front panel, and just to the side of them on the circuit board. The test pins are marked TP1..TP8 on the silk screen. The top LED of the eight (which is yellow) indicates the state of test pin one (1). When the test pin voltage is LO, the LED turns on. When it is HI (3.3V), the LED turns off. You can look at the test pin voltages with an oscilloscope by hooking the probe onto one of the pins, and grounding the probe to one of the two ground pins below the test pins.

Test pins TP1 to TP8 have the following functions when the test-pin configuration switches (TPC0 and TPC1) are set to zero. The test pins have other functions for other settings of TPC0 and TPC1, but these change with every version of the firmware. If you would like to know their functions for your particular firmware version, we will be glad to let you know.

| Test Point | Logic Signal (Asserted when LO) |

| 1 | Pixel Clock |

| 2 | Line Clock |

| 3 | Delay Timer Not Zero |

| 4 | Control Data Strob |

| 5 | Convert for 8-Bit ADC, Convert for 16-Bit ADC, or CLAMP\ |

| 6 | Measuring Loop Time |

| 7 | Transmitting Device Addres |

| 8 | Transmitting Device Command |

The A2037E alters the A2037A test pin use so that it can provide Ethernet link and activity indicators.

| Test Point | Logic Signal, Asserted when LO |

| 1 | (Ethernet Link Detected by RCM2200) XOR (Configuration Switch Pressed) |

| 2 | Ethernet Activity on the RCM2200 |

| 3 | Pixel Clock |

| 4 | Line Clock |

| 5 | Delay Timer Not Zero |

| 6 | Repeat Counter Not Zero |

| 7 | Transmitting Device Address |

| 8 | Transmitting Device Command |

We use the test pins to help us find problems with LWDAQ components. We can, for example, trigger an oscilloscope off the Pixel Counter Clock or Line Counter Clock and look at the signals on an image sensor head.

[24-MAR-23] After we apply power to the A2037E, the RCM2200 embedded eight-bit microprocessor module boots up and starts its TCPIP communication stack to provide a LWDAQ server. The A2037E is ready to communicate a few seconds after power-up or harware reset by the front panel reset button. When operating with its default configuration, the A2037E listens for a TCPIP connection on port 90 of IP address 10.0.0.37. It services only one connection at a time, but starting with software version 15, it will accept any number of connections and service them in turn. Earlier versions of the software will reject any second attempt to connect by a LWDAQ client. By means of the Configurator Tool in our LWDAQ Software, we change the port and IP address of our A2037E.

The A2037E accepts communication based in the LWDAQ message protocol. Here are the message identifiers recognised by the A2037E TCPIP interface, as implemented in the program that runs in the RCM2200 module. This program is written in C. The latest version of the code will be here. The C program is called C2037Exx.c, where xx is the version number. The binary files we upload to the RCM2200 are C2037Exx.bin.zip. The first time we boot up the RCM2200, we hold down the configuration switch on the back of the A2071E to format its EEPROM file system and write default values to the configuration file.

| ID | Function | SV |

| 0 | version_read | 1 |

| 1 | byte_read | 1 |

| 2 | byte_write | 1 |

| 3 | stream_read | 1 |

| 4 | data_return | 1 |

| 5 | byte_poll | 4 |

| 6 | login | 7 |

| 7 | config_read | 7 |

| 8 | config_write | 7 |

| 9 | mac_read | 7 |

| 10 | stream_delete | 9 |

| 11 | echo | 9 |

| 12 | stream_write | 9 |

| 13 | reboot | 9 |

The LWDAQ Software uses Tcl to open a TCPIP socket to the A2037E and transmit messages. It uses Tcl to receive message back from the A2037E. The Tcl routines that implement the LWDAQ TCPIP Messaging Protocol are in a file called Driver.tcl, which is one of the scripts in our LWDAQ distribution. You will find our software here.

The byte_write execution time on the A207E is 400 μs minimum and 510 μs on average when including the time it takes to transmit the instructions to the RCM2200 over TCPIP. The transfer rate from the A2037E's RAM to the RCM2200's RAM is 700 kByte/s. The overall data transfer rate from A2037E RAM to a data acquisition computer is 160 kByte/s. The stream delete rate when clearing the driver memory is 1.0 MByte/s.

The A2037A is a VME slave. It responds to all address cycles in its 512 kByte address space. Following the assertion of the VME backplane data strobes, the A2037A takes 350 ns to assert DTACK. The assertion of DTACK on a read cycle means that data is ready on the backplane data lines. On a write cycle it means the data written to the board has been received, and the cycle is over. When the backplane !SYSRESET signal is asserted, the A2037A resets itself.

A2037A: Here are the modifications required by various versions of the A2037A.

A2037E: Here are the modifications required by various versions of the A2037E.

The A2037 is a large circuit by our standards: there are 160 components of 56 different types. Its functions are varied and complex. Here is a list of the most common ciruit failures.

| Symptom | Cause | Cure |

|---|---|---|

| power lights flashing | failure of a 10 μF tantalum capacitor | replace capacitor presents 0 Ω |

| failure to respond on cold days (A only) | timing conflict in firmware version 10 | re-program with firmware version 11 |

| one driver socket does not work | faulty DG411 from Harris Semiconductor | replace faulty DG411 beside socket |

| cannot write configuration file (E only) | error on A2055 piggy-back board | join pins of P3 together with solder lump |

| bad power supply readings | problem in power supply monitors | use P8 test input, see below |

When we test a driver, we start by testing the power supply monitors with the Diagnostic Instrument (Power-Monitor Test). We should see the power supplies at ±15 V and +5 V. The common-mode gain should be less than ±0.2 V/V and differential gain should be 62±3 V/V. We attempt to capture images from the driver sockets with a camera like the A2056 (Eight-Bit Test). We try measuring temperatures with a device like the A2053 (Sixteen-Bit Test). We acquire temperatures from all driver sockets (All-Socket Test).

Suppose the board passes the Eight-Bit Test, the Sixteen-Bit Test and the All-Socket Test, but fails the Power-Monitor test. There is a problem in the power monitor circuit. We connect a ±100 mV sin wave to P8. We open the Voltmeter Instrument and select driver socket zero and multiplexer socket zero. We should see our sin wave amplified by roughly ×55. If the input is ±100 mV, the Voltmeter should show an rms amplitude of 3.9 V. If the sin wave does not look right, check the pins on U14, especially the right side. One of the bits in the sixteen-bit word might be missing. Increase the frequency and see if the 10-kHz low-pass filter in front of the sixteen-bit ADC works properly. If you don't see the sin wave, follow it through the switches, resistors, and op-amps to see where it disappears. You will find a bad joint or a broken component.

Note: All our schematics and Gerber files are distributed under the GNU General Public License.

All code is in the Code Directory.

Driver Checker: A LWDAQ Tool that checks RAM and data acquisition with a graphical user interface.